# **Test and Measurement Performance Report**

Part Number TM7SSSH22S8MS028 (Core HC)

**Distribution**: Internal and External Use

| REVISION:            | ECN INFORMATION:  EC No: N/A  DATE: 04/ 12 / 2021 | TITLE: Core HC 2.5 | ation SHEET No.  1 of 21 |                                     |

|----------------------|---------------------------------------------------|--------------------|--------------------------|-------------------------------------|

| DOCUMEN <sup>-</sup> | T NUMBER:                                         | SI ENGINEER:       | DESIGN ENGINEER          | ENGINEERING MANAGER                 |

| RSI-TM7SSSH22S8MS028 |                                                   | R.Stavoli          | H.Tran E.Soubl           |                                     |

|                      |                                                   |                    | TEMP                     | LATE FILENAME: SPMISIZE A1(V.1).DOC |

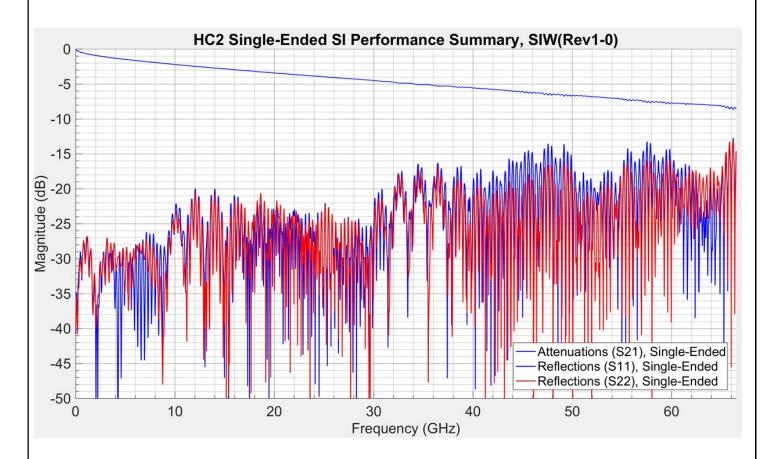

SI Performance Summary (Attenuation & Reflections, Substrate Integrated Waveguide/SIW, Single-Ended)

\* For further details regarding the testing setup and configuration please see the rest of the report.

| REVISION:            | ECN INFORMATION:    | TITLE: Core HC 2.5mm SIW: Configuration |                       |                       | SHEET No. |

|----------------------|---------------------|-----------------------------------------|-----------------------|-----------------------|-----------|

| 4                    | EC No: N/A          | 1X2P (HC2 to PCB)                       |                       | <b>2</b> of <b>21</b> |           |

| •                    | DATE: 04/ 12 / 2021 | CARLISLE IT CON                         | •                     |                       | 20121     |

| DOCUMENT             | ΓNUMBER:            | SI ENGINEER:                            | DESIGN ENGINEER       | ENGINEERIN            | G MANAGER |

| RSI-TM7SSSH22S8MS028 |                     | R.Stavoli                               | R.Stavoli H.Tran E.So |                       | ubh       |

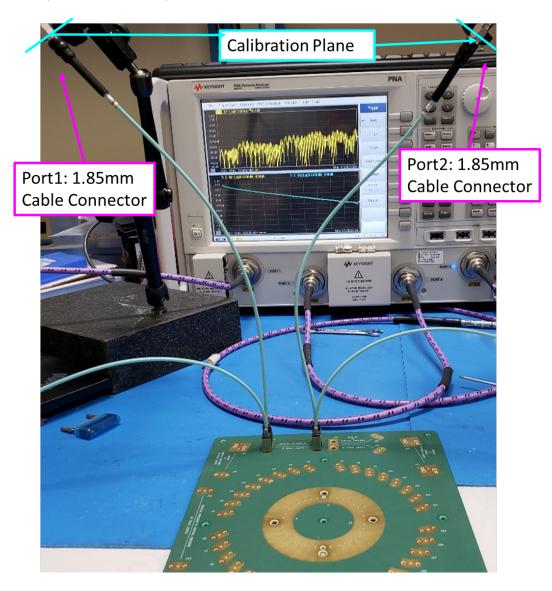

#### 1.0 TEST SETUP AND DUT

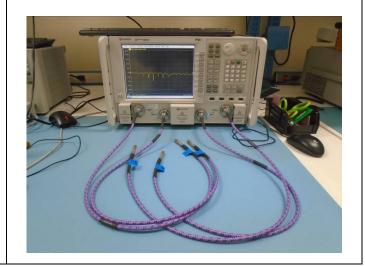

#### Equipment, fixtures, and methods

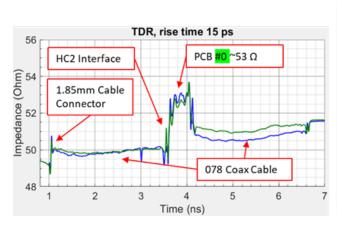

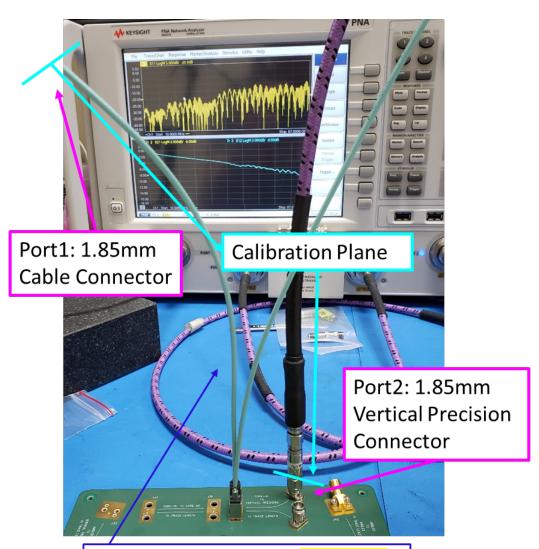

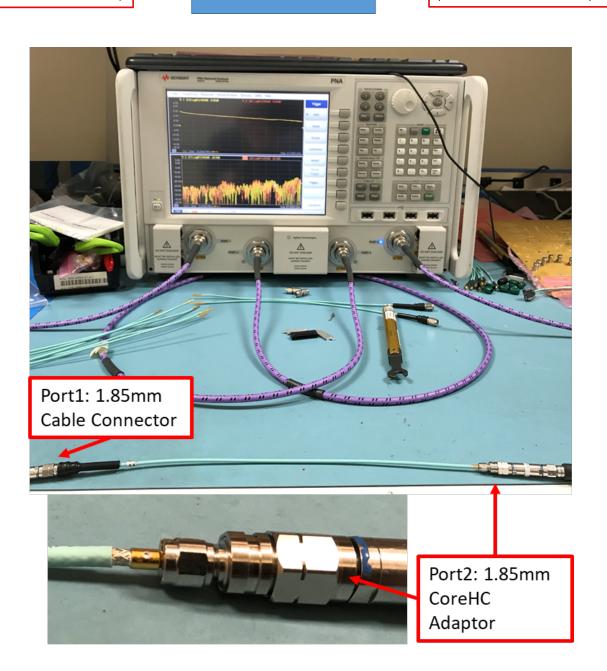

**Test method:** All data measured from test PCB shown below and a N5227A PNA Network Analyzer

- Calibration was performed up to the 1.85mm SMA adapters using calibration kit: 85058B

- Data was swept from 10 MHz to 67GHz for 6700 points

- Data averaging was turned off.

- Data is not dembedded and includes the board traces and the Core HC cable assembly

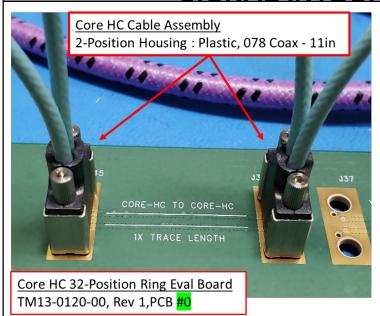

#### Assembly Description

- T&M PN: TM7SSSH22S8MS028

- 2- Position LCP Connector Housing, two pieces at the interface

- <u>11-inch solid center conductor 092 coax</u> cable

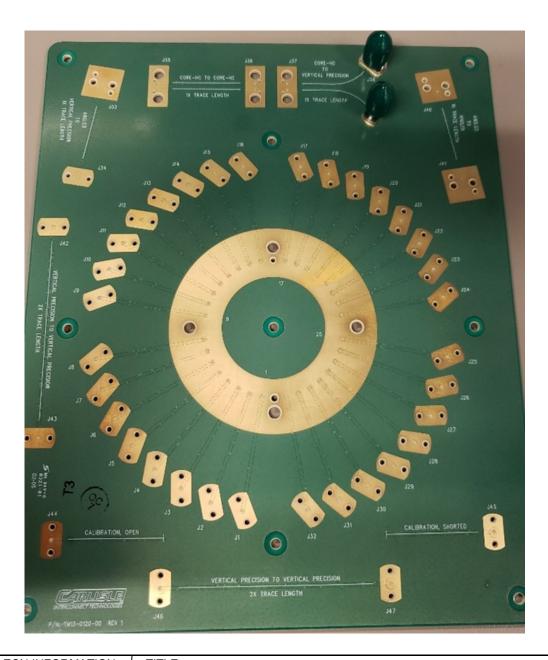

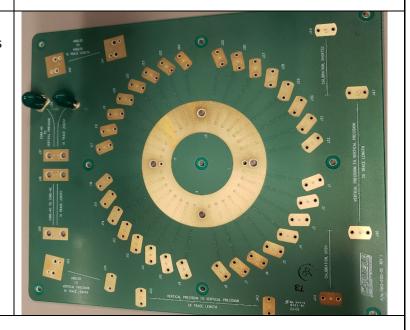

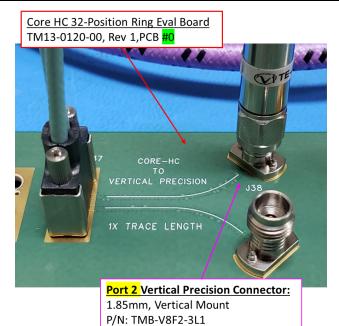

- Carlisle DUT PCB: TM13-0120-00

Core HC 32-position eval board, SIW, Vertical Launch, Rev 1, #0

- Port 1: 1.85mm Cable Connector (Core HC)

- Port 2: 1.85mm Cable Connector (Core HC) or 1.85mm Stripline Vertical Launch Precision Connector (on HC2, SIW PCB)

| Testing | ı Samı | oles: |

|---------|--------|-------|

|---------|--------|-------|

- 4 Samples 2 THRU Measurements w/ PCB, Core HC2 → Core HC2

- 4 Channels

2 Crosstalk Meas. w/PCB (FEXT, NEXT), HC2 → HC2

- 1 THRU Measurements w/ PCB, HC2 → 1.85mm Vertical Precision Connector

- 2 THRU Meas. w/RF Adaptor (2 Chan. x 1 samples)

| REVISION:            | ECN INFORMATION: EC No: N/A  DATE: 04/ 12 / 2021 | Core HC 2.5mm SIW: Configuration 1X2P (HC2 to PCB) CARLISLE IT CONFIDENTIAL |  |             | 3 of 21         |

|----------------------|--------------------------------------------------|-----------------------------------------------------------------------------|--|-------------|-----------------|

| DOCUMENT NUMBER:     |                                                  | SI ENGINEER: DESIGN ENGINEER ENGINEERIN                                     |  | ENGINEERING | <u> MANAGER</u> |

| RSI-TM7SSSH22S8MS028 |                                                  | R.Stavoli H.Tran E.S                                                        |  | E.So        | u <b>bh</b>     |

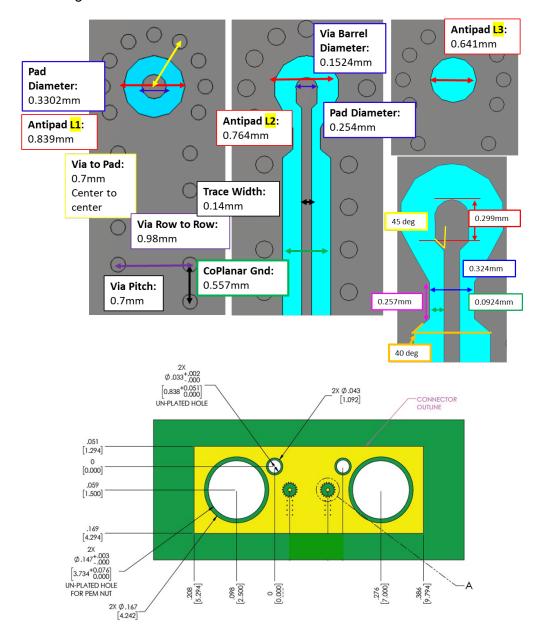

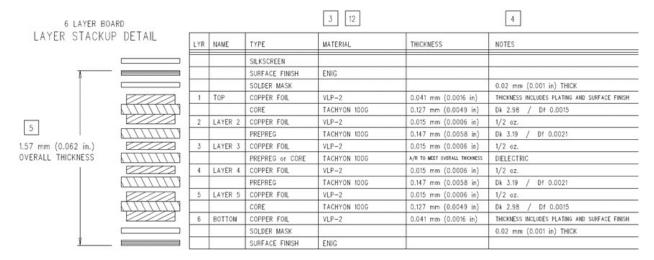

#### 2.0 BOARD STACKUP & FOOTPRINT INFORMATION

- TM13-0120-00 Carlisle Core HC 32-Position, SIW Test Board

- o Revision 1, #0, Substrate Integrated Waveguide(SIW), Vertical Launch

- Cable Assembly placed on 2-Position Single-Ended Footprint

- Dielectric Material: Tachyon 100G (Dk.2.98, Df 0.0015 @ 20 GHz)

- L1 Core Thickness: L1: 0.127mm / 5 mil

- L2 PrePreg Thickness: L2: 0.149mm / 5.9mil

0

| <u> </u> | 1                    | ECN INFORMATION:  EC No: N/A  DATE: 04/ 12 / 2021 | Core HC 2.5n<br>1X2P (HC2 to<br>CARLISLE IT CON | 4 of 21        |                                     |

|----------|----------------------|---------------------------------------------------|-------------------------------------------------|----------------|-------------------------------------|

|          | DOCUMENT NUMBER:     |                                                   | SI ENGINEER: DESIGN ENGINEER ENGINEERIN         |                | ENGINEERING MANAGER                 |

|          | RSI-TM7SSSH22S8MS028 |                                                   | R.Stavoli                                       | H.Tran E.Soubh |                                     |

|          |                      |                                                   |                                                 | TEMF           | LATE FILENAME: SPM[SIZE_A](V.1).DOC |

#### C) PCB FINISH

#### 1. Surface Protective Plating

- a. All exposed copper on the outer layers shall be plated with a protective surface finish.

- b. All exposed pads, edge fingers and plated through holes shall be ENIG with thickness listed in Table 2.

#### **Table 2: Protective Plating Thickness**

| Nickel         | ickel Immersion Gold |                |            |

|----------------|----------------------|----------------|------------|

| μm (microinch) |                      | μm (microinch) |            |

| Min.           | Max.                 | Min.           | Max.       |

| 2.5 (100)      | 13(512)              | 0.051(2)       | 0.2032 (8) |

| REVISION:            | ECN INFORMATION: EC No: N/A  DATE: 04/ 12 / 2021 | Core HC 2.5mm SIW: Configuration 1X2P (HC2 to PCB) CARLISLE IT CONFIDENTIAL |                 |                    | SHEET No. 5 of 21  |

|----------------------|--------------------------------------------------|-----------------------------------------------------------------------------|-----------------|--------------------|--------------------|

| DOCUMEN <sup>*</sup> | T NUMBER:                                        | SI ENGINEER:                                                                | DESIGN ENGINEER | ENGINEERING        | G MANAGER          |

| RSI-TM7SSSH22S8MS028 |                                                  | R.Stavoli                                                                   | H.Tran E.Soubh  |                    | ubh                |

|                      |                                                  |                                                                             | TEMP            | LATE FILENAME: SPM | I[SIZE_A](V.1).DOC |

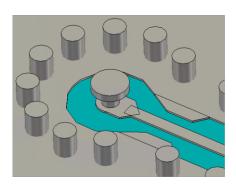

#### 3.0 SIMULATION RESULTS, SUBRTRATE INTEGRATED WAVEGUIDE, SINGLE-ENDED

#### Diameter:

Signal Pad (L1): 0.3302mm/13mil Antipad (L1): 0.839mm/33.07mil Signal Pad (L2): 0.254mm/10mil Finish Via: 0.1524mm/6mil

| REVISION:            | ECN INFORMATION: | Core HC 2.5mm SIW: Configuration        |   |                       | SHEET No. |

|----------------------|------------------|-----------------------------------------|---|-----------------------|-----------|

| 4                    | EC No: N/A       | 1X2P (HC2 to PCB)                       |   | <b>6</b> of <b>21</b> |           |

| DATE: 04/ 12 / 2021  |                  | CARLISLE IT CO                          | • |                       | 0 01 2 1  |

| DOCUMENT NUMBER:     |                  | SI ENGINEER: DESIGN ENGINEER ENGINEERIN |   | ENGINEERING           | G MANAGER |

| RSI-TM7SSSH22S8MS028 |                  | R.Stavoli H.Tran E.So                   |   | ubh                   |           |

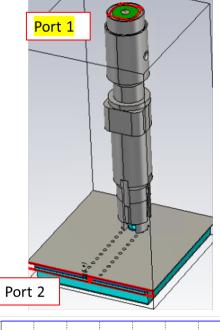

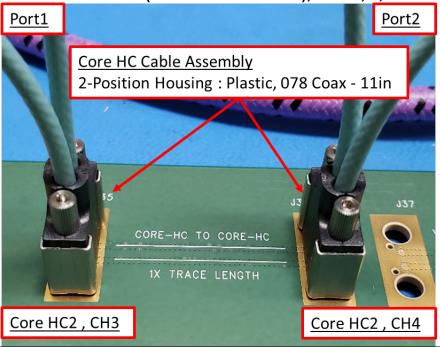

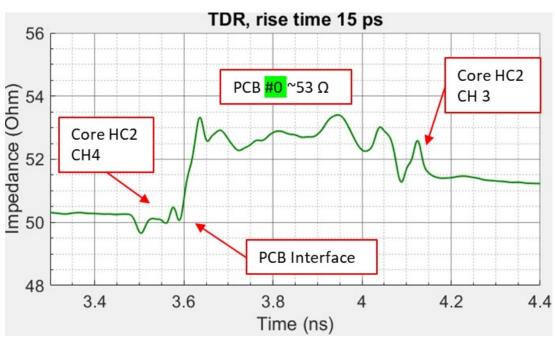

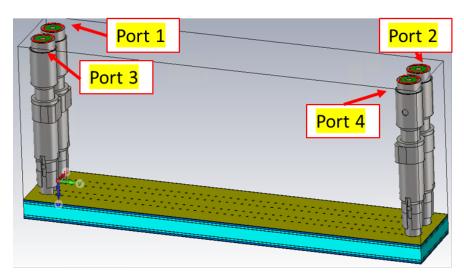

#### 4.0 MEASUREMENT SET-UP, CORE HC2 → HC2, SINGLE-ENDED (HC2 SIW REV1 PCB)

Port 1: Core HC (1.85mm Cable Connector)

Device Under Test

Port 2: Core HC (1.85mm Cable Connector

Measurements are not dembedded and include the **Core HC assemblies** (cable connector, cable, interconnect), PCB (transitions, traces)

| REVISIO 1                     | EC                   | N INFORMATION: No: N/A TE: 04/ 12 / 2021 | Core HC 2.5mm SIW: Configuration 1X2P (HC2 to PCB) CARLISLE IT CONFIDENTIAL |             |                        | 7 of 21    |           |

|-------------------------------|----------------------|------------------------------------------|-----------------------------------------------------------------------------|-------------|------------------------|------------|-----------|

| DOCUN                         | DOCUMENT NUMBER:     |                                          | <u>S</u>                                                                    | I ENGINEER: | <u>DESIGN ENGINEER</u> | ENGINEERIN | G MANAGER |

| RSI-T                         | RSI-TM7SSSH22S8MS028 |                                          |                                                                             | R.Stavoli   | H.Tran                 | E.Soubh    |           |

| TEMPLATE FILENAME: SPM[SIZE_/ |                      |                                          | //[SIZE_A](V.1).DOC                                                         |             |                        |            |           |

Core HC2, 2-Position Footprint

#### Pad Geometry:

Signal Pad Diam.(L1): 0.3302mm/13mil Antipad Diam.(L1): 0.839mm/33.07mil Signal Pad Diam.(L2): 0.254mm/10mil Finish Via Diam: 0.1524mm/6mil

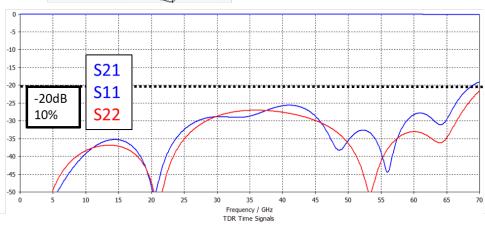

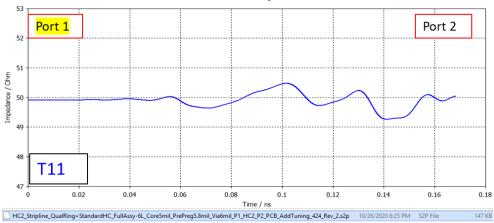

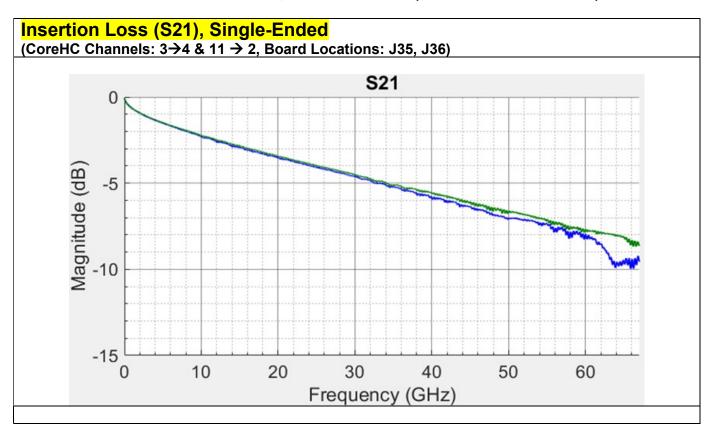

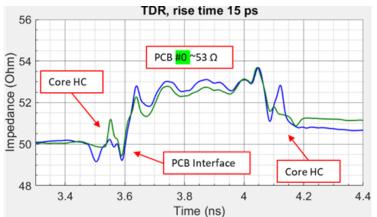

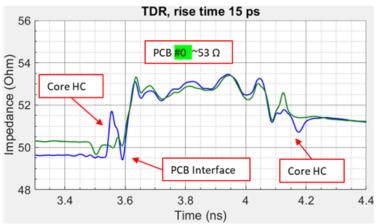

#### 5.0 SIGNAL INTEGRITY RESULTS, SINGLE-ENDED (HC2 SIW REV1 BOARD)

| REVISION:            | ECN INFORMATION:  EC No: N/A  DATE: 04/ 12 / 2021 | Core HC 2.5mm SIW: Configuration 1X2P (HC2 to PCB) CARLISLE IT CONFIDENTIAL |  |                 | 8 of 21            |                    |

|----------------------|---------------------------------------------------|-----------------------------------------------------------------------------|--|-----------------|--------------------|--------------------|

| DOCUMEN              | T NUMBER:                                         | SI ENGINEER:                                                                |  | DESIGN ENGINEER | ENGINEERIN         | G MANAGER          |

| RSI-TM7SSSH22S8MS028 |                                                   | R.Stavoli                                                                   |  | H.Tran          | E.Soubh            |                    |

|                      |                                                   |                                                                             |  | TEMP            | LATE FILENAME: SPN | I[SIZE_A](V.1).DOC |

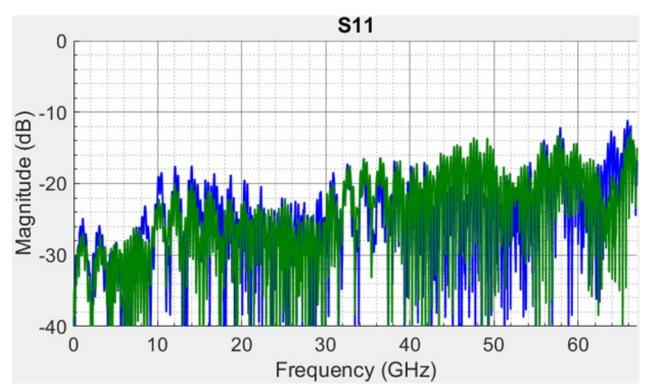

# Return Loss (S11), Single-Ended

(CoreHC Channels: 3→4 & 11 → 2, Board Locations: J35, J36)

| REVISION:            | ECN INFORMATION: EC No: N/A DATE: 04/ 12 / 2021 | Core HC 2.5mm SIW: Configuration 1X2P (HC2 to PCB) CARLISLE IT CONFIDENTIAL |                 |                      | 9 of 21          |

|----------------------|-------------------------------------------------|-----------------------------------------------------------------------------|-----------------|----------------------|------------------|

| DOCUMEN <sup>-</sup> | T NUMBER:                                       | SI ENGINEER:                                                                | DESIGN ENGINEER | ENGINEERING          | MANAGER          |

| RSI-TM7SSSH22S8MS028 |                                                 | R.Stavoli                                                                   | H.Tran E.Soubh  |                      | ıbh              |

|                      |                                                 |                                                                             | TEMF            | LATE FILENAME: SPM[S | SIZE_A](V.1).DOC |

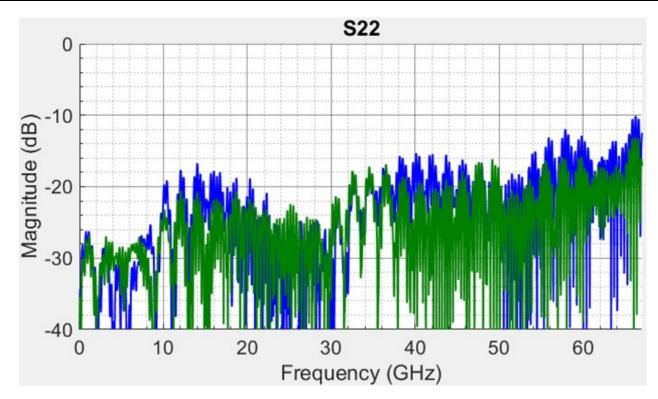

# Return Loss (S22), Single-Ended

(CoreHC Channels: 3→4 & 11 → 2, Board Locations: J35, J36)

| REVISION:            | ECN INFORMATION: EC No: N/A  DATE: 04/ 12 / 2021 | Core HC 2.5n 1X2P (HC2 to CARLISLE IT CON | 10 of 21        |                                     |

|----------------------|--------------------------------------------------|-------------------------------------------|-----------------|-------------------------------------|

| DOCUMENT             | ΓNUMBER:                                         | SI ENGINEER:                              | DESIGN ENGINEER | ENGINEERING MANAGER                 |

| RSI-TM7SSSH22S8MS028 |                                                  | R.Stavoli                                 | H.Tran          | E.Soubh                             |

|                      |                                                  |                                           | TEME            | LATE EILENAME: COMICIZE AI/V 1) DOC |

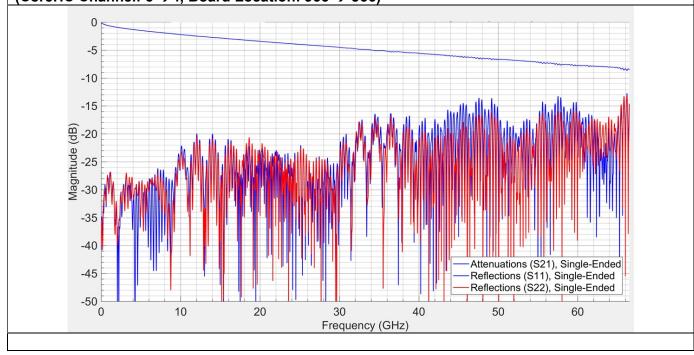

6.0 SIGNAL INTEGRITY RESULTS (HC2 SIW REV1 PCB), CH #3, 4, LOCATION J35-36

(CoreHC Channel: 3 →4, Board Location: J35 → J36)

| 1                    | ECN INFORMATION:  EC No: N/A  DATE: 04/ 12 / 2021 | 1X2P (HC2 to | Core HC 2.5mm SIW: Configuration 1X2P (HC2 to PCB) CARLISLE IT CONFIDENTIAL |                     |  |  |

|----------------------|---------------------------------------------------|--------------|-----------------------------------------------------------------------------|---------------------|--|--|

| DOCUMENT NUMBER:     |                                                   | SI ENGINEER: | DESIGN ENGINEER                                                             | ENGINEERING MANAGER |  |  |

| RSI-TM7SSSH22S8MS028 |                                                   | R.Stavoli    | H.Tran E.Soubh                                                              |                     |  |  |

|                      |                                                   |              | TEMPLATE FILENAME: SPM[SIZE_A](V.1).DOC                                     |                     |  |  |

(CoreHC Channel: 3 →4, Board Location: J35 → J36)

| REVISION:            | ECN INFORMATION:  EC No: N/A  DATE: 04/ 12 / 2021 | Core HC 2.5n 1X2P (HC2 to CARLISLE IT CON | •                      | 12 of 21                            |

|----------------------|---------------------------------------------------|-------------------------------------------|------------------------|-------------------------------------|

| DOCUMENT NUMBER:     |                                                   | SI ENGINEER:                              | <u>DESIGN ENGINEER</u> | ENGINEERING MANAGER                 |

| RSI-TM7SSSH22S8MS028 |                                                   | R.Stavoli                                 | H.Tran E.Soubh         |                                     |

|                      |                                                   |                                           | TEMP                   | LATE FILENAME: SPM[SIZE_A](V.1).DOC |

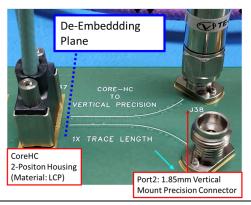

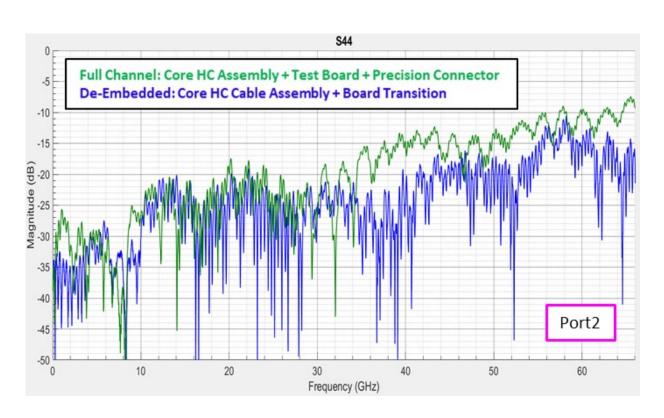

# 7.0 MEASUREMENT SET-UP, DE-EMBEDDING: CORE HC ightarrow 1.85 VERTICAL PREC. CONNECTOR

Port 1: Core HC (1.85mm Cable Connector)

**Device Under Test**

Port 2: 1.85mm Vertical Mount Precision Connector (TMB-V8F2-3L1)

Core HC Cable Assembly (Channel 3)

2-Position Housing : Plastic

092D Coax - 11in

| REVISION:            | ECN INFORMATION:                         | TITLE: Core HC 2 5n | TITLE: Core HC 2.5mm SIW: Configuration |                    |                        |  |  |

|----------------------|------------------------------------------|---------------------|-----------------------------------------|--------------------|------------------------|--|--|

| 4                    | EC No: N/A                               | 1X2P (HC2 to        |                                         | ation              | <b>13</b> of <b>21</b> |  |  |

| <b>'</b>             | DATE: 04/ 12 / 2021                      | CARLISLE IT CON     | •                                       |                    | 130121                 |  |  |

| DOCUMEN <sup>-</sup> | T NUMBER:                                | SI ENGINEER:        | DESIGN ENGINEER                         | ENGINEERING        | <u>G MANAGER</u>       |  |  |

| RSI-TM7              | I-TM7SSSH22S8MS028 R.Stavoli H.Tran E.Sc |                     | ubh                                     |                    |                        |  |  |

|                      |                                          |                     | TEMF                                    | LATE FILENAME: SPM | [SIZE_A](V.1).DOC      |  |  |

J37 CORE-HC

TO

VERTICAL PRECISION

J38

1X TRACE LENGTH

J39

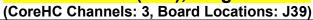

# Insertion Loss (S21), Single-Ended

| 1                    | ECN INFORMATION:  EC No: N/A  DATE: 04/ 12 / 2021 | 1X2P (HC2 to | Core HC 2.5mm SIW: Configuration 1X2P (HC2 to PCB) CARLISLE IT CONFIDENTIAL |                                     |  |  |  |  |

|----------------------|---------------------------------------------------|--------------|-----------------------------------------------------------------------------|-------------------------------------|--|--|--|--|

| DOCUMENT NUMBER:     |                                                   | SI ENGINEER: | DESIGN ENGINEER                                                             | ENGINEERING MANAGER                 |  |  |  |  |

| RSI-TM7SSSH22S8MS028 |                                                   | R.Stavoli    | H.Tran E.Soubh                                                              |                                     |  |  |  |  |

|                      |                                                   |              | TEMF                                                                        | LATE FILENAME: SPM[SIZE_A](V.1).DOC |  |  |  |  |

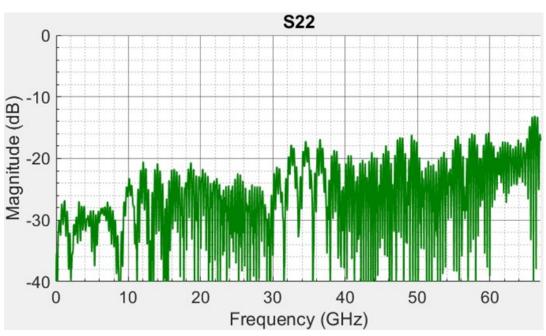

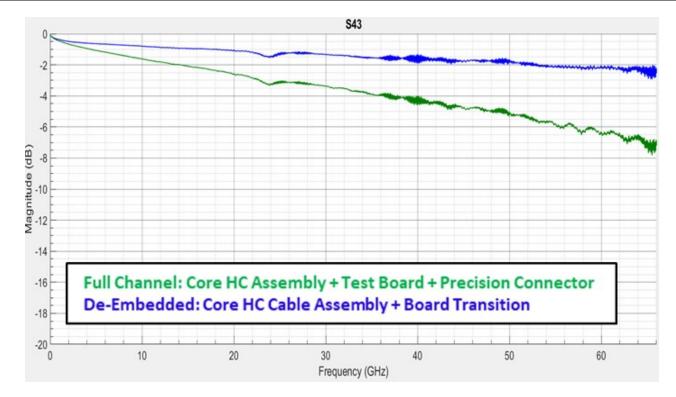

# Return Loss (S22), Single-Ended

(CoreHC Channels: 3, Board Locations: J39)

| REVISION:            | ECN INFORMATION:  EC No: N/A  DATE: 04/ 12 / 2021 | Core HC 2.5n 1X2P (HC2 to CARLISLE IT CON | •                      | 15 of 21                            |

|----------------------|---------------------------------------------------|-------------------------------------------|------------------------|-------------------------------------|

| DOCUMENT NUMBER:     |                                                   | SI ENGINEER:                              | <u>DESIGN ENGINEER</u> | ENGINEERING MANAGER                 |

| RSI-TM7SSSH22S8MS028 |                                                   | R.Stavoli                                 | H.Tran E.Soubh         |                                     |

|                      |                                                   |                                           | TEMP                   | LATE FILENAME: SPM[SIZE_A](V.1).DOC |

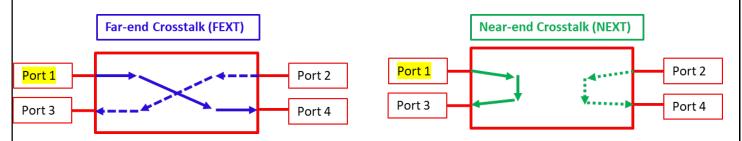

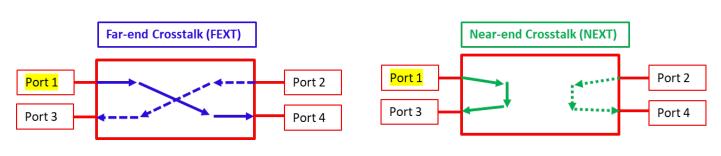

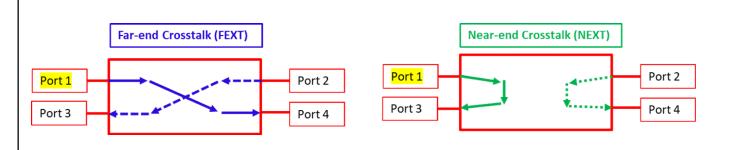

## 8.0 MEASUREMENT SET-UP, SINGLE-ENDED, CROSSTALK (HC2 SIW REV1)

| REVISION:            | ECN INFORMATION:  EC No: N/A  DATE: 04/ 12 / 2021 | 1X2P (HC2 to | Core HC 2.5mm SIW: Configuration 1X2P (HC2 to PCB) CARLISLE IT CONFIDENTIAL |                    |                   |  |  |

|----------------------|---------------------------------------------------|--------------|-----------------------------------------------------------------------------|--------------------|-------------------|--|--|

| DOCUMENT NUMBER:     |                                                   | SI ENGINEER: | <u>DESIGN ENGINEER</u>                                                      | ENGINEERING        | <u>G MANAGER</u>  |  |  |

| RSI-TM7SSSH22S8MS028 |                                                   | R.Stavoli    | H.Tran E.Soubh                                                              |                    | ubh               |  |  |

|                      |                                                   |              | TEMP                                                                        | LATE FILENAME: SPM | [SIZE_A](V.1).DOC |  |  |

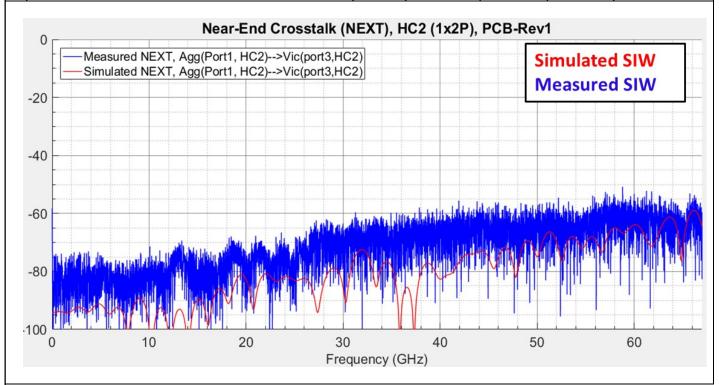

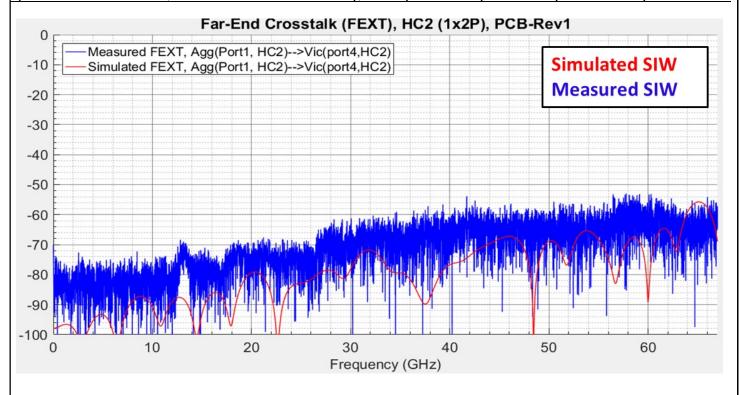

9.0 SIGNAL INTEGRITY RESULTS, SINGLE-ENDED, CROSSTALK (HC2 SIW REV1)

#### Near-End Crosstalk (S31), Single-Ended

(CoreHC Channels: 3, 11, Board Locations: J35), Port1(HC2-CH11) → Port3(HC2-CH3)

| REVISION:            | ECN INFORMATION: EC No: N/A DATE: 04/ 12 / 2021 | 1X2P (HC2 to                            | •      | ation       | 17 of 21       |

|----------------------|-------------------------------------------------|-----------------------------------------|--------|-------------|----------------|

| DOCUMENT NUMBER:     |                                                 | SI ENGINEER: DESIGN ENGINEER ENGINEERIN |        | ENGINEERING | <u>MANAGER</u> |

| RSI-TM7SSSH22S8MS028 |                                                 | R.Stavoli                               | H.Tran | E.Soi       | ubh            |

#### Far-End Crosstalk (S41), Single-Ended

(CoreHC Channels:11, Board Locations: J35/J36), Port1(HC2-CH11) → Port 4 (VMSIW/PCB)

| REVISION:            | ECN INFORMATION:                | TITLE: Core HC 2.5n                     | Core HC 2.5mm SIW: Configuration           |             |         |  |

|----------------------|---------------------------------|-----------------------------------------|--------------------------------------------|-------------|---------|--|

| 1                    | EC No: N/A  DATE: 04/ 12 / 2021 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \   | 1X2P (HC2 to PCB) CARLISLE IT CONFIDENTIAL |             |         |  |

| DOCUMENT NUMBER:     |                                 | SI ENGINEER: DESIGN ENGINEER ENGINEERIN |                                            | ENGINEERING | MANAGER |  |

| RSI-TM7SSSH22S8MS028 |                                 | R.Stavoli H.Tran E.So                   |                                            | ubh         |         |  |

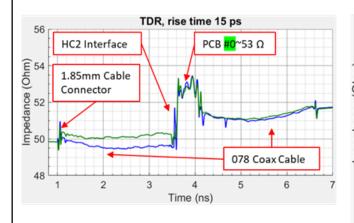

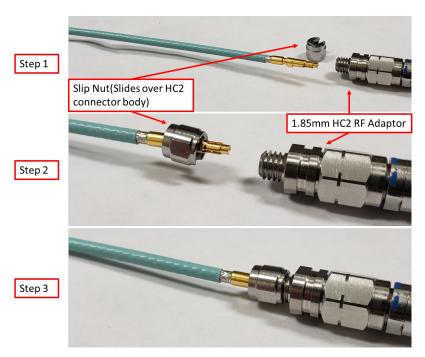

## 10.0 MEASUREMENT SET-UP (HC2 1.85MM RF ADAPTOR #1)

Port 1: Core HC (1.85mm Cable Connector)

Device Under Test

Port 2: Core HC Interface (1.85mm RF Core HC Adaptor #1)

| REVISION:            | ECN INFORMATION:    | TITLE: Core HC 2.5n | nm SIW: Configur                      | ation SHEET No.                     |

|----------------------|---------------------|---------------------|---------------------------------------|-------------------------------------|

| 4                    | EC No: N/A          | 1X2P (HC2 to        |                                       | 19 of 21                            |

| •                    | DATE: 04/ 12 / 2021 | CARLISLE IT CON     | · · · · · · · · · · · · · · · · · · · | 130121                              |

| DOCUMENT             | NUMBER:             | SI ENGINEER:        | DESIGN ENGINEER                       | ENGINEERING MANAGER                 |

| RSI-TM7SSSH22S8MS028 |                     | R.Stavoli           | H.Tran E.Soubh                        |                                     |

|                      |                     |                     | TEMP                                  | LATE FILENAME: SPM[SIZE_A](V.1).DOC |

# **HC2 Adaptor Testing Procedure**

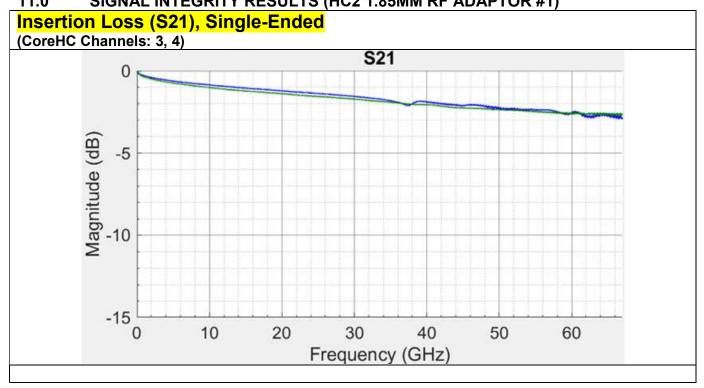

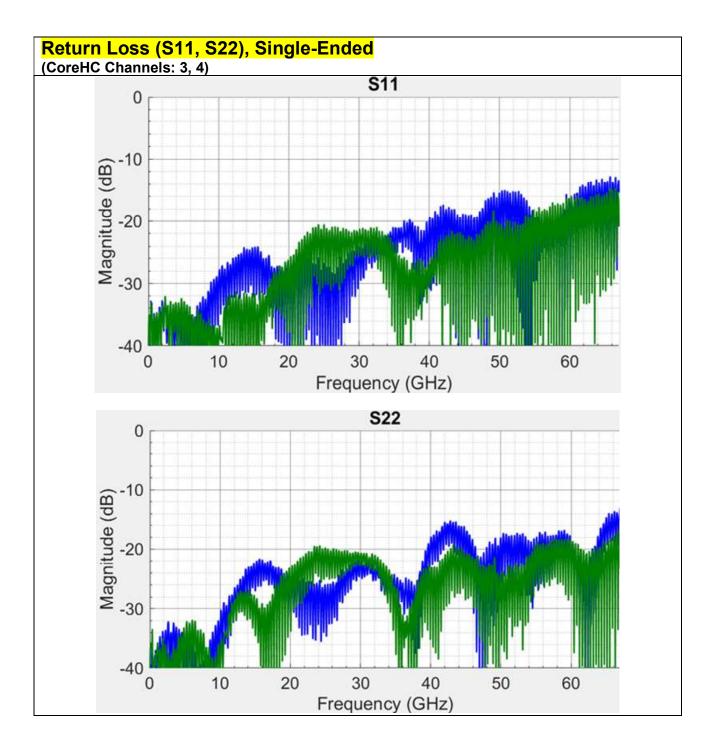

#### 11.0 SIGNAL INTEGRITY RESULTS (HC2 1.85MM RF ADAPTOR #1)

| 1                    | ECN INFORMATION:  EC No: N/A  DATE: 04/ 12 / 2021 | 1X2P (HC2 to                                          | Core HC 2.5mm SIW: Configuration 1X2P (HC2 to PCB) CARLISLE IT CONFIDENTIAL |                     |  |  |  |

|----------------------|---------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------|---------------------|--|--|--|

| DOCUMENT NUMBER:     |                                                   | SI ENGINEER: <u>DESIGN ENGINEER</u> <u>ENGINEERIN</u> |                                                                             | ENGINEERING MANAGER |  |  |  |

| RSI-TM7SSSH22S8MS028 |                                                   | R.Stavoli                                             | H.Tran E.Soubh                                                              |                     |  |  |  |

|                      |                                                   |                                                       | TEMPLATE FILENAME: SPM[SIZE_A](V.1).DOC                                     |                     |  |  |  |

# 12.0 APPENDIX, (SPARAMETERS SHOWN IN REPORT) CoreHC Reference Cable Assembly\_SIW\_2-Position Measurements 041221 4/12/202:

| _ Cole IC Kel        | erence Cable Assembly_51W_2-F | USICION IN EASONETHERICS_041221 | 4/12/2021 7.34 FIVI | Compressed (zipp | J, 143 KD              |

|----------------------|-------------------------------|---------------------------------|---------------------|------------------|------------------------|

| REVISION:            | ECN INFORMATION:              | TITLE: Core HC 2                | imm SIW: Configu    | ration           | SHEET No.              |

| 4                    | EC No: N/A                    | 1X2P (HC2                       | •                   |                  | <b>21</b> of <b>21</b> |

| •                    | DATE: 04/ 12 / 2021           | CARLISLE IT CO                  | •                   | '                | 210121                 |

| DOCUMENT NUMBER:     |                               | SI ENGINEER:                    | DESIGN ENGINEER     | ENGINEERING      | <u>MANAGER</u>         |

| RSI-TM7SSSH22S8MS028 |                               | R Stavoli                       | H Tran              | F Sout           | nh                     |